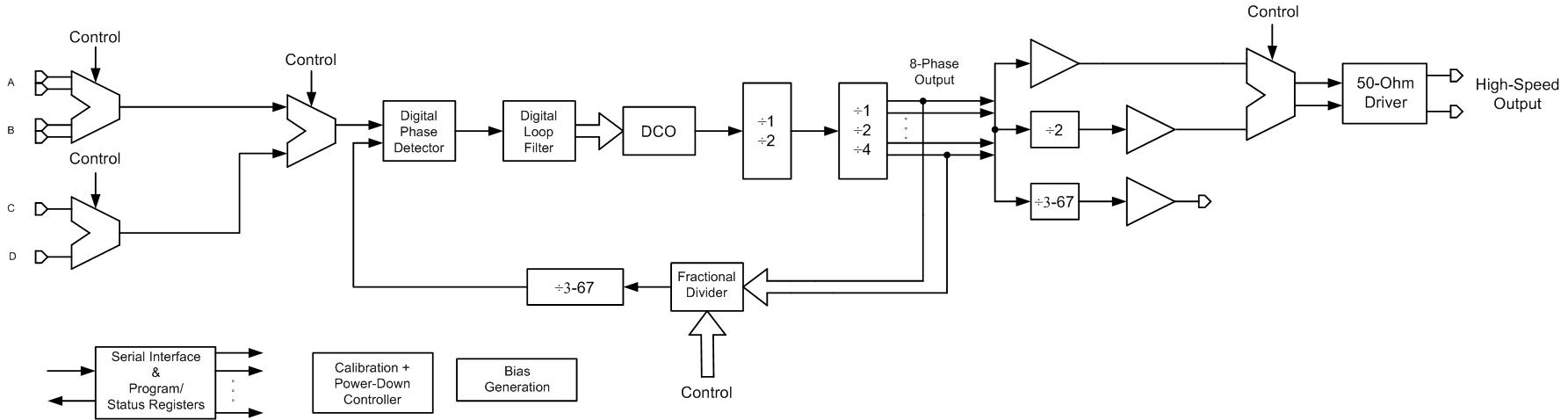

| Granite SemicCom's Digital PLL is intended for applications such the Clock-Multiplying-Unit in a SERDES or a Clock-Driver with fractional-N division capability. It has been realized in TSMC's 40G technology. It does not require off-chip components, is highly reconfigurable, and has very good jitter performance (with on-chip accummulated jitter measurement). It is high speed, can be programmed over a wide range (guaranteed 0.5-7.5 GHz output), is low in power (32 mW at 5GHz), requires only a minimal silicon area, and includes an output driver capable of driving off-chip into 50 ohms at full-speed. Since most of the high-speed circuitry is digital, it is also readily customizable and portable to other technologies. |

|